文章摘要

随着半导体制程技术向2nm节点逼近,单纯依赖电子互连已无法平衡大规模算力与功耗控制的矛盾,AI大模型训练驱动数据中心向百万级GPU规模演进,进一步让芯片间、机架间高速通信遭遇带宽与散热瓶颈。共封装光学(CPO)成为半导体行业突破电互连物理极限的战略级演进方向,该技术通过将光引擎与计算ASIC共同封装,能量消耗仅为传统可插拔光模块的1/3.5,还可将GPU集群的计算利用率提升20%以上。但高度集成的光电融合架构给测试带来“黑盒挑战”,传统以硬件为中心的单一功能测试设备无法适配高集成度验证需求,迫切需要可灵活演进的数字化可重构测试架构。

Liquid Instruments开发的Moku平台,通过“可重构硬件+软件定义仪器”架构实现测试范式升级,依托高性能FPGA的实时处理能力,将16种以上精密仪器整合到单一硬件内核,大幅压缩测试系统物理体积。这种架构的核心优势在于其数字化互连能力,Moku:Delta利用内部高达160 Gb/s的数字总线,使信号在不同仪器槽位间流转无需外接电缆,彻底消除了由外部线缆引入的相位偏移、噪声与寄生效应,搭配专利混合ADC采样技术,可提供极低信号底噪,适配半导体微弱光电信号的表征需求。该平台支持动态重构测试配置,可通过多仪器并行测试降低成本、提升效率,还能随需求迭代灵活扩展方案。

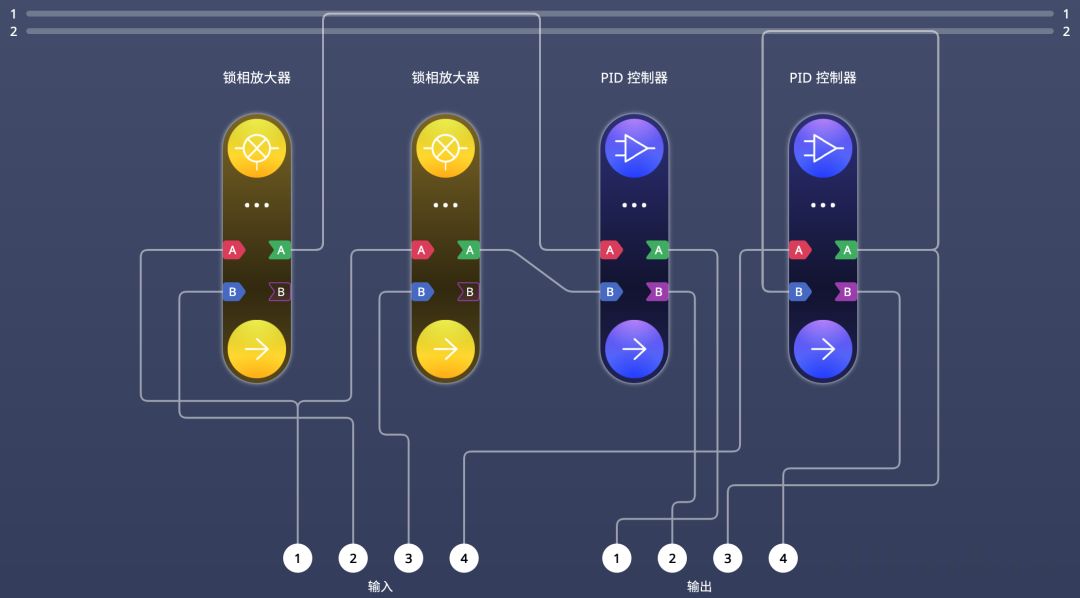

在英特尔实验室的硅基光电异质集成研究中,需要为片上多个相位调制器寻找最优偏置条件,传统方案面对多维度调优任务,复杂度与耗时呈指数增长,当控制维度持续增加时,测试系统本身必须具备动态重构与自动化闭环能力,才能匹配器件复杂度的增长。研究团队借助Moku的多仪器并行模式,在单一硬件上同时运行多个锁相放大器与PID控制器,将原本需要数百步骤收敛的扫描任务压缩至几次迭代即可完成,大幅提升验证与协作效率。AMD在量产失效分析场景中,利用Moku的可重构特性灵活切换测试方案、优化信号处理链路,还可部署预训练神经网络实现AI赋能的深度降噪,将信噪比提升约16倍,有效提升缺陷检测效率。“可重构硬件+软件定义”的测试架构,正在成为高集成度芯片验证的重要方向,Moku平台可根据任务需求动态重构测试能力,大幅降低多设备拼接带来的系统复杂度与空间开销,重新定义了AI与CPO时代半导体测试的效率上限。Liquid Instruments将携全系列Moku产品亮相慕尼黑上海光博会,其首席执行官将在展会论坛分享AI与测试测量融合的最新成果。

原文和模型

【原文链接】 阅读原文 [ 3133字 | 13分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 doubao-seed-2-0-lite-260215

【摘要评分】 ★★★☆☆