文章摘要

【关 键 词】 CFET架构、imec研究、逻辑节点、器件集成、工艺优化

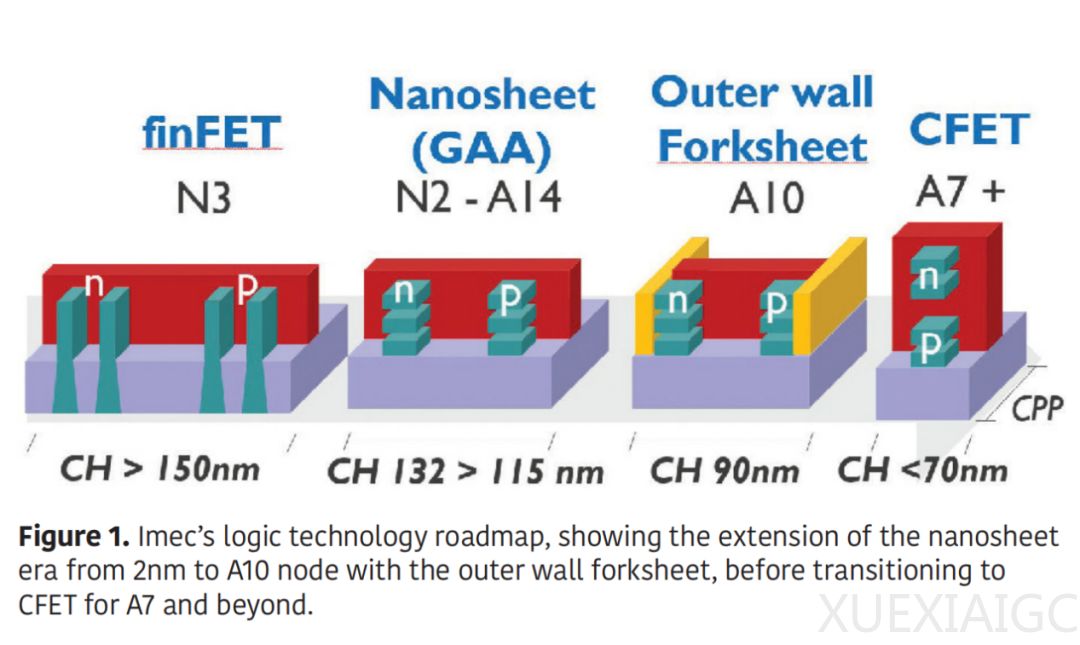

互补型场效应晶体管(CFET)器件架构有望在逻辑技术路线图中取代环栅(GAA)纳米片晶体管,其中单片CFET(mCFET)因干扰最小、可快速落地被视为关键方向。它通过垂直堆叠n型和p型MOS晶体管,首次消除标准单元高度中n-p间距的限制,若结合先进接触与供电技术,可大幅缩小逻辑标准单元尺寸。不过垂直堆叠带来隔离挑战,需专用模块实现,比如中间介质隔离(MDI)模块可隔离顶部与底部栅极,为不同器件设置不同阈值电压。近年mCFET集成流程关键模块进展显著,imec在2024年VLSI大会展示了与内部间隔层兼容的带MDI模块mCFET,同年IEDM大会实验演示了底部pMOS源漏极背面直接接触的功能性mCFET,预计在逻辑技术路线图的A7节点(0.7nm)引入mCFET,取代外壁叉片架构。

imec提出双排CFET架构是A7节点标准单元集成的最优方式,通过设计技术协同优化(DTCO)研究证实其能平衡制造能力与面积效率。但业界因巨额工具投资和额外风险对新架构持谨慎态度,跨节点可扩展性成为关键。imec通过模拟15级环形振荡器评估A7、A5、A3节点的功率-性能-面积(PPA)指标,发现标准单元缩小会降低有效驱动电流、增加寄生电容,需针对性性能提升措施:A5节点需引入外壁叉片架构以增强沟道应力、降低寄生电容;A3节点除Ω形栅极外壁叉片和M0电源轨外,需引入混合沟道取向,最佳组合可将驱动电流提高高达20%,以此平衡性能与功率密度。

imec在IEDM 2025上实验演示了嵌入式MDI(eMDI)模块,可集成不同沟道取向的mCFET器件。该模块通过晶圆熔合键合,将分别生长的n、pMOS外延堆叠结合,SiCN键合介质作为嵌入式隔离层。相比传统替代MDI(rMDI),eMDI可集成异质沟道(不同取向、应变或材料)以优化器件性能,还能降低工艺复杂性、简化外延步骤、提升设计灵活性,只需少量修改即可集成到mCFET基线。目前imec正优化eMDI关键模块,未来计划集成不同沟道材料,并采用类似“嵌入式”方法开发底部介质隔离层(eBDI),eBDI有望简化背面连接集成,还可选用高导热材料缓解mCFET热可靠性担忧。

原文和模型

【原文链接】 阅读原文 [ 2520字 | 11分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 doubao-seed-1-8-251228

【摘要评分】 ★★★☆☆