文章摘要

【关 键 词】 A14工艺、台积电领先、三星竞争、Rapidus跟进、先进制程挑战

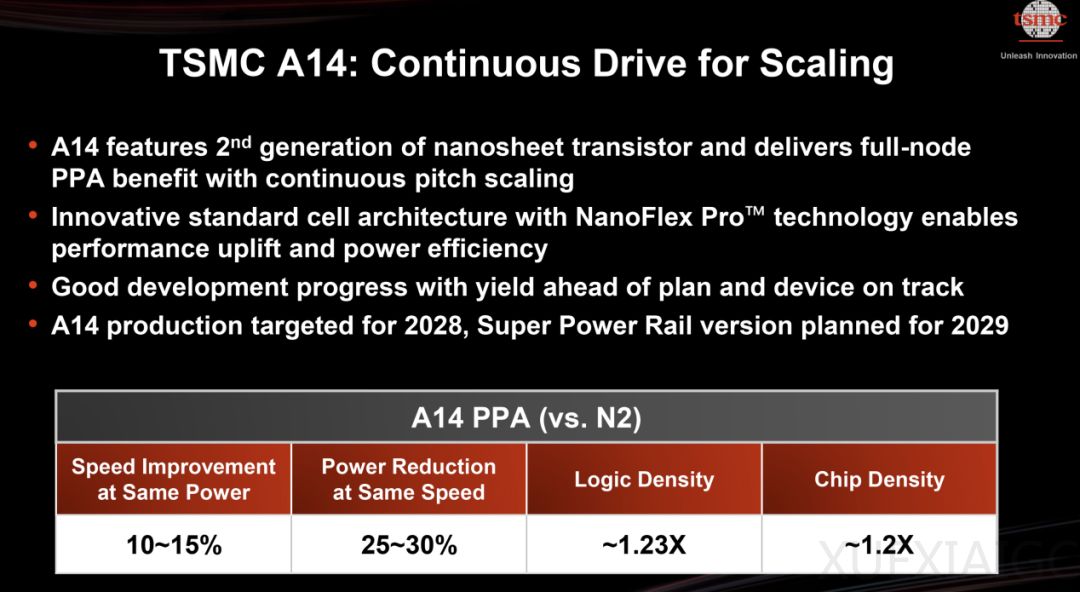

台积电已正式确认其下一代晶圆代工工艺命名为“A14”,定位为1.4nm级超精细工艺,计划于2027年底在台湾中部科学园区Fab 25晶圆厂启动试生产,2028年实现全面量产。该工艺基于第二代纳米片晶体管架构(GAAFET),相较于现有2nm工艺(N2),在相同功耗下性能提升15%,功耗最多降低30%,逻辑密度提高超过20%。A14还引入NanoFlex Pro设计协同优化技术,支持灵活配置晶体管以适配不同应用负载,但初期版本暂不支持背面供电网络(BSPDN),仅适用于无需高密度电源布线的客户端、边缘及特殊应用;预计2029年将推出带SPR背面供电的A14P版本,并进一步开发最高性能版A14X与成本优化版A14C。

台积电采取“分阶段导入”光刻设备策略:初期借助现有低数值孔径EUV配合多重曝光保障良率与成本,2027年第三季度后逐步过渡至ASML高数值孔径EUV,体现其“稳定领先”的技术路径。此节奏使其在与英特尔、三星的竞争中占据时间优势——三星已将1.4nm工艺量产目标延至2029年,而三星与Rapidus亦正加速推进1nm工艺研发:三星目标2030年前量产,依托“Fork Sheet”新结构升级GAA器件;Rapidus则计划2026年底开始2nm测试芯片试产,2027年进入量产阶段,力求在1nm节点上将与台积电的技术差距压缩至六个月以内。

在更底层制造环节,先进节点面临显著挑战:金属层图案化与材料复杂性呈指数增长,晶体管从FinFET迈向环栅纳米片带来三维结构跃升,器件特征缩至几个原子尺度,微小缺陷即可能影响热迁移与可靠性;晶圆减薄至10微米厚度导致形变风险升高,需精密处理堆叠对准问题;异构集成已成为主流解决方案,例如英特尔采用Foveros微凸点与混合键合技术实现3D封装,其连接间距已降至9微米;谷歌、特斯拉等系统厂商依赖多芯片组架构扩展性能,但伴随互连效应、调试难度和良率压力增加。业界普遍认为单芯片扩展已趋极限,多芯片系统成为主流方向,其中桥接器方案较大型中介层更具经济性。

面对极端尺寸下的系统复杂性,行业正转向动态裕量管理策略——不再依赖静态保护带,而是通过实时监测时序裕量应对工艺偏差与老化影响;软硬件协同、算法量化及高速互连整合共同提升能效;同时,如Lam Research等企业推动干式光刻胶与高NA EUV等突破性工具组合,持续支撑尺寸继续缩小。值得注意的是,随着公差收紧,制造过程各环节变异控制愈发关键,早期介入设计、环境参数监控与全流程仿真已成标准流程。

在2nm及以下制程中,几乎所有挑战都相互关联,孤立解决可能引发次生难题;当前节点的功耗优化并非单纯靠缩小晶体管,而是依赖架构重构与集成创新;异构封装、3D IC及新型互联技术虽潜力巨大,但散热、翘曲与信号完整性的工程实现仍是重大瓶颈;未来节点发展不仅取决于物理尺寸,更由功耗、性能、面积与成本的综合演进所定义。尽管技术演进已进入前所未有的高维复杂阶段,相关产业仍保有充足投入动力持续推进边界拓展。

原文和模型

【原文链接】 阅读原文 [ 7426字 | 30分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3-vl-flash-2026-01-22

【摘要评分】 ★★★★★