文章摘要

【关 键 词】 HBM、产能不足、生产难点、封装瓶颈、良率控制

当前HBM(高带宽显存)是市场热议话题,围绕供应短缺、HBM产能不足拖累GPU生产的讨论随处可见,但很少有内容深入拆解其生产全流程的核心难点,相关内容基于亲身经历与公开技术资料,覆盖从设计、制造、测试、封装到交付后全环节的挑战,HBM是半导体价值链中唯一一个每个环节都同时面临最高难度的产品,这是其价格昂贵、供应稀缺的核心原因,即便克服生产难题,还受限于上游封装产能,进一步推高了稀缺性。

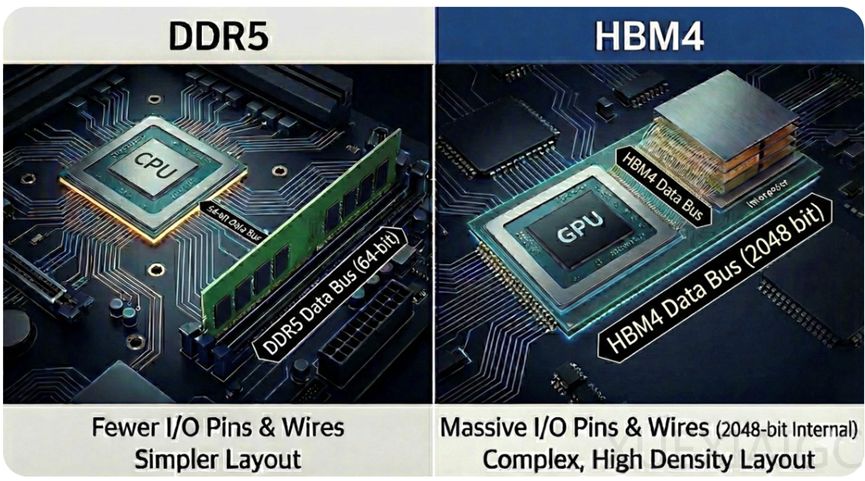

设计环节,HBM总线宽度远高于传统DDR5,HBM3E达1024位,HBM4更是提升至2048位,单颗堆叠需要上千个连接,无法在PCB实现布线,因此必须依赖硅中介层与CoWoS这类2.5D封装技术;通过TSV为十余个堆叠芯片分配纯净电源是极易被忽视的核心挑战,上层芯片电压降问题严重,TSV布局方案是内存厂商核心专有技术,直接决定良率与性能,没有公开信息;HBM4采用代工厂级逻辑工艺制造底层基片,可承载客户定制逻辑电路,不同客户的HBM4将成为不同物理结构的产品,内存正式从通用组件转向半定制,设计复杂度大幅提升。制造环节核心难点是良率控制,TSV加工难度高,一个12层堆叠包含数百万个TSV,单个缺陷就会导致整颗芯片报废,堆叠要求将单个晶圆减薄至30-50微米,不到头发丝直径的一半,随着层数增加减薄压力持续增大;按比特计算,HBM消耗的晶圆面积约为传统DRAM的两到三倍,晶圆厂分配产能给HBM会挤压DDR5、LPDDR等其他内存的产能,当前其他内存市场的供应紧张是这种产能权衡的结构性结果。测试环节,堆叠前必须完成已知良品芯片测试来控制整体成本,堆叠后缺陷定位难度随层数增加呈指数增长,测试基础设施更新跟不上HBM更快的迭代节奏,测试成本在总制造成本中占比很高。

封装环节是当前半导体领域最精密的组装工艺,微凸点错位就会导致连接失效,混合键合是长远发展方向,但量产良率、可靠性问题还未解决,堆叠层数增加还会加剧翘曲问题,影响下游组装与长期可靠性;完成HBM堆叠后还需通过台积电CoWoS工艺与GPU集成,当前台积电CoWoS产能已售罄至2026年,是整个AI芯片供应链最紧缺的环节。交付后仍有诸多挑战,客户组装的热应力可能引发原有合格产品故障,数据中心满负荷运行下存在电迁移、热循环疲劳、焊点蠕变三种长期失效机制,现有封装后修复功能仅能解决部分缺陷,HBM发生现场故障后,因为集成在同一封装内无法内部探测,存在归因难、无现成测试方案、供应商现场支持能力不足等问题,会消耗大量时间与资源。

原文和模型

【原文链接】 阅读原文 [ 3487字 | 14分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 doubao-seed-2-0-lite-260215

【摘要评分】 ★★★☆☆