文章摘要

【关 键 词】 EDA、LLM应用、硬件设计、自动化、芯片测试

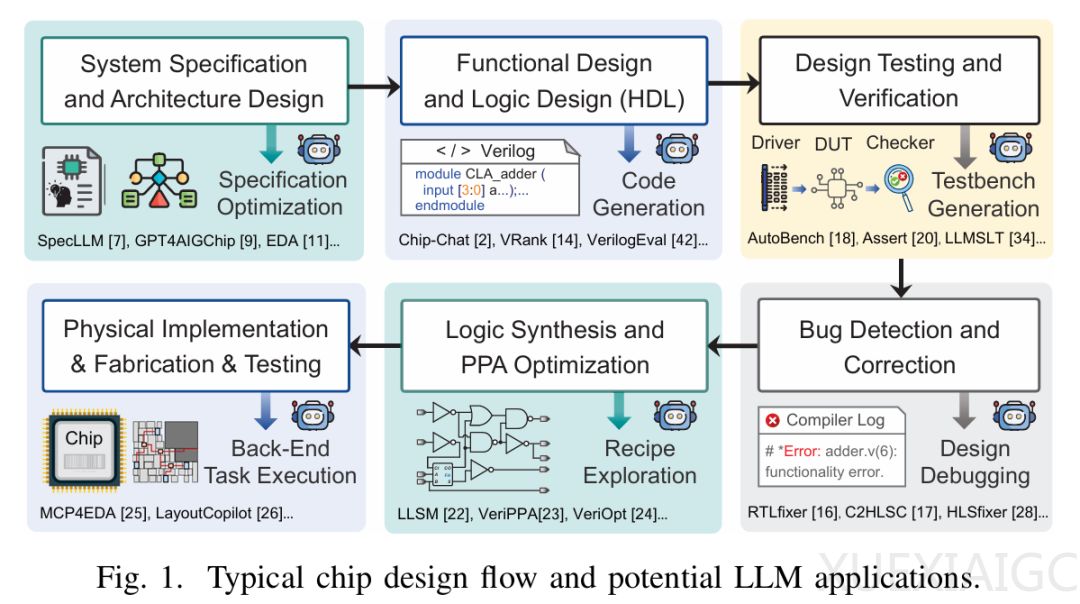

随着集成电路复杂度的提升,电子设计自动化(EDA)领域正面临人力密集型工作流程的转型需求。硬件开发过程中大量迭代环节不仅效率低下且易出错,而大型语言模型(LLM)在语境理解和文本生成方面的突破为EDA革新提供了新机遇。由于硬件描述语言(HDL)和设计脚本的文本属性与LLM能力高度契合,这种技术融合有望实现从被动辅助到主动智能体的范式转变,覆盖规格优化、硬件生成等全流程任务。

当前LLM在EDA的应用已形成三大核心方向:前端设计、高级综合(HLS)和验证测试。在硬件设计领域,Chip-Chat通过GPT-4完成了8位微处理器的全流程HDL流片;GPT4AIGChip采用模块化解耦技术实现AI加速器自动化开发;VRank等工具则利用LLM的概率特性生成多方案择优。HLS领域涌现出C2HLSC等框架,通过工具引导反馈将C程序迭代转换为HLS兼容版本,HLS-Repair则融合检索增强生成技术提升代码质量。测试验证环节,AutoBench构建了自校正测试平台,AssertLLM通过信号映射生成形式化断言,显著提升缺陷检测效率。

LLM辅助的HLS工作流展现出四阶段创新架构。预处理阶段通过编译器错误检测与LLM潜在问题识别实现双重筛查;检索增强生成阶段整合专业修正模板提升修复精度;等价验证阶段采用C-RTL协同仿真确保功能一致性;最终PPA优化阶段通过编译指示调整实现性能突破。针对HLS行为差异问题,新型测试框架引入谱图监测和LLM驱动的测试输入生成,结合冗余过滤技术将仿真效率提升40%。

硬件设计领域正经历从微调模型到全自动化的技术演进。早期DAVE模型仅能处理教科书级Verilog问题,VeriGen系列通过海量开源代码训练达到商用水平。ChatGPT-4在Chip-Chat中首次实现完整流片验证,推动研发重点转向结构化提示框架。最新AutoChip系统集成树搜索算法,通过EDA工具反馈实现设计迭代优化,在VerilogEval基准测试中展现50%的无干预成功率。CL-Verilog等模型进一步采用模块化分层设计,可生成密码学加速器等复杂应用。

系统级测试(SLT)自动化取得突破性进展。针对边际缺陷检测难题,研究人员开发出基于Code Llama的功耗优化框架,采用结构化思维链提示技术生成高质量C代码。通过动态温度调节和莱文斯坦距离保障代码多样性,该方案在24小时内生成2021个候选片段,最优结果达到5.042瓦功耗,较传统遗传算法提升11.3%能效比。

未来发展方向聚焦多模态智能代理构建。突破性解决方案需整合自然语言、HDL代码和物理布局数据,建立统一表征体系以捕捉设计意图。关键挑战包括:弥合高层抽象与硬件实现间的语义鸿沟,通过专家知识库训练提升HLS质量,开发高层引导的RTL调试工具,以及构建隐私安全的本地化部署方案。这些创新将推动EDA从工具集合向自主智能体转型,最终实现”规格到硅片”的全流程自动化。

原文和模型

【原文链接】 阅读原文 [ 7382字 | 30分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★★