文章摘要

【关 键 词】 芯片制造、3D NAND、存储器技术、半导体材料、二维晶体管

芯片制造行业正面临需求激增与技术进步放缓的双重挑战。一方面,逻辑芯片、DRAM和NAND闪存的需求旺盛,产能受限可能引发设备供应短缺;另一方面,摩尔定律的物理极限使尺寸缩小和性能提升变得困难。尽管如此,行业仍通过创新技术寻求突破,包括3D NAND垂直堆叠、新型互连材料和二维晶体管等方向。

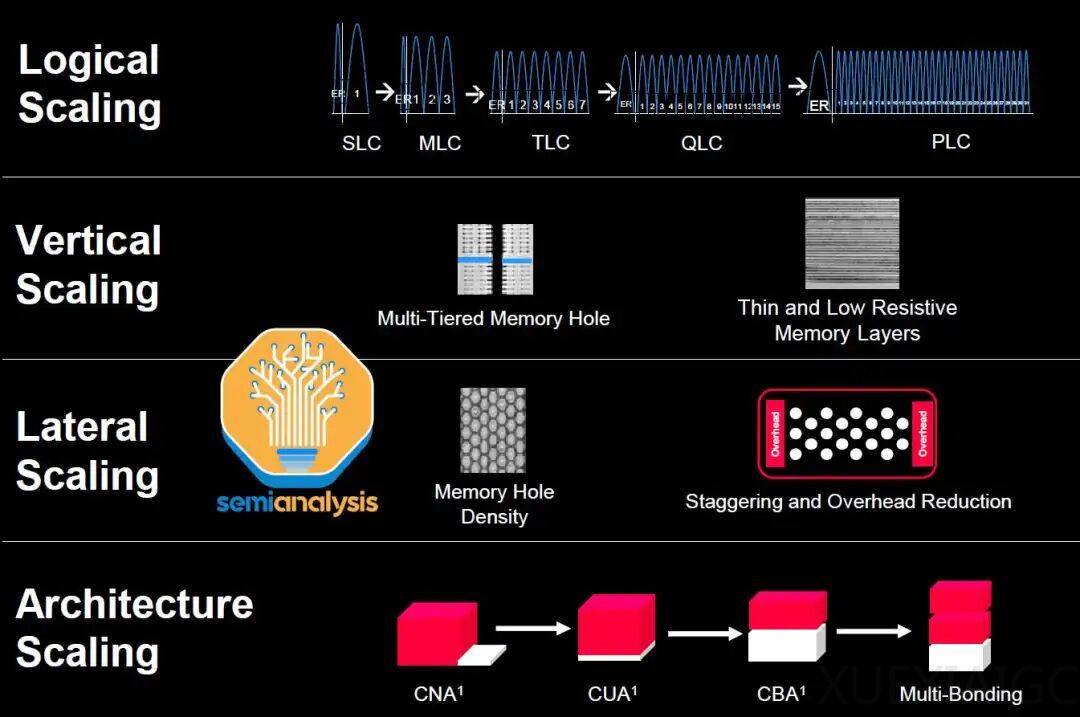

3D NAND技术成为应对存储需求的关键路径。当前领先工艺已实现3xx层堆叠,单片12英寸晶圆可生产超过30TB容量。SK海力士的321层工艺较前代提升44%存储密度,但面临良率与成本挑战。技术扩展依赖四个维度:逻辑缩放(每单元位数)、垂直扩展(堆叠层数)、横向缩放(单元尺寸)和架构优化。其中垂直扩展因成本效益成为主流,但层数增加导致晶圆应力累积和蚀刻难度指数级上升,海力士采用低应力材料和局部强制控制技术应对。值得注意的是,三星通过将字线金属从钨替换为钼,使接触电阻降低40%,读取时间缩短30%,展现了材料创新的潜力。

存储单元架构创新呈现突破性进展。SK海力士研发的5比特/单元技术通过分割沟道为半圆柱体区域,将阈值电压状态从32种简化为36种组合,显著提升存储密度。但这种复杂结构面临制造成本高的瓶颈。与此同时,三星和铠侠等企业通过三层堆叠架构继续推进密度竞争,其中铠侠BiCS10的QLC密度可达37Gb/mm²。

互连材料革命正在10纳米以下节点展开。传统铜互连因尺寸效应面临电阻率飙升问题,钌成为替代选择。三星采用晶粒取向工程使钌线电阻降低46%,IMEC则规划了从铜到钌的过渡路线图,预计在16纳米间距节点实现全自对准通孔技术。该技术通过气隙结构和双重图案化工艺,解决超微尺寸下的可靠性和RC延迟问题。

二维材料为晶体管微缩提供新路径。过渡金属二硫化物(TMD)因其大带隙特性可抑制10纳米以下栅长的隧穿漏电,但面临三大产业化障碍:首先是300毫米晶圆级集成难题,IMEC的干法转移技术试图解决薄膜均匀性问题;其次是接触电阻瓶颈,需要实现在工作电压下Rc<100Ω·µm的目标;最后是p型器件性能不足,费米能级钉扎效应导致空穴注入效率低下。台积电研究表明,通过氮基中间层工程可将WSe₂空穴迁移率提升至100cm²/V·s以上,但亚阈值摆幅仍劣于硅基器件。此外,层数控制缺陷和缺乏可靠掺杂技术进一步制约发展,当前解决方案倾向于功函数工程替代传统掺杂。

技术突破越来越依赖全产业链协同。从海力士的沟道蚀刻设备、Lam公司的钌沉积工具,到IMEC的EUV光刻路线,制造设备的进步直接决定工艺可行性。同时,二维器件需要建立专属的TCAD模型和仿真工具链,以弥补现有硅基参数体系的不足。这些发展表明,半导体行业已进入需要材料、设备、设计协同创新的系统竞争阶段,单个技术节点的突破越来越依赖于整个生态体系的成熟度。

原文和模型

【原文链接】 阅读原文 [ 6953字 | 28分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★★