文章摘要

【关 键 词】 台积电、晶体管技术、集成电路、半导体、芯片制造

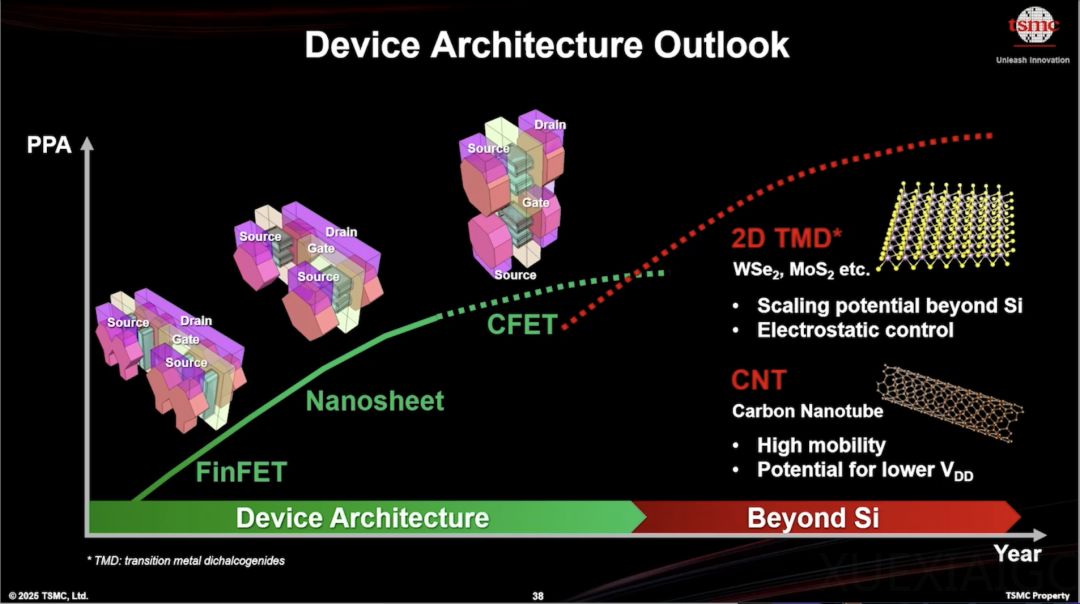

在IEDM 2025大会上,台积电首次公开了基于互补场效应晶体管(CFET)技术的集成电路运行成果,标志着该技术从器件级优化迈向电路级集成的关键转折。CFET通过垂直堆叠n沟道和p沟道FET,理论上可将晶体管密度较现有纳米片FET提升近一倍,但技术难度极高。此次台积电展示了两项核心突破:一是全功能101级3D单片CFET环形振荡器,工作电压范围0.5V至0.95V,振荡频率随电压升高而稳定;二是全球最小的6T SRAM位单元,采用高密度(HD)和高电流(HC)两种设计,其中HD型面积比纳米片FET单元缩小30%,HC型读取电流达HD型的1.7倍。

技术实现上,台积电通过纳米片切割隔离(NCI)技术将栅极间距压缩至48nm以下,并在SRAM单元中创新采用对接接触(BCT)互连实现反相器交叉耦合。电学测试显示,HD型SRAM在0.75V电压下读取静态噪声容限为135mV,写入容限达265mV,但参数仍有优化空间。CFET技术预计在2030年代投入实际应用,目前仍处于早期研发阶段,需解决制造复杂性、供电架构和高纵横比结构带来的工艺挑战。

行业动态方面,英特尔和三星也在加速CFET布局。英特尔2023年推出采用背面供电技术的反相器,接触多晶硅间距(CPP)缩小至60nm;三星则实现48nm CPP器件,并通过干法刻蚀工艺将良率提升80%。IBM与三星合作开发的阶梯式沟道设计进一步缓解了堆叠高度问题。imec预测,到2032年CFET将成为突破1纳米节点的关键,但需结合芯粒和先进封装技术弥补纳米片架构的微缩瓶颈。

未来发展中,互连技术升级是台积电的重点方向,包括铜互连的过孔方案优化、新型阻挡层开发,以及气隙金属和插层石墨烯等材料的应用。尽管CFET面临成本与工艺挑战,业界普遍认为其是延续摩尔定律的必经之路,需通过EDA工具提前布局和集成方案创新来降低产业化风险。

原文和模型

【原文链接】 阅读原文 [ 2947字 | 12分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★☆