文章摘要

【关 键 词】 人工智能、三维存储、制造工艺、单片架构、堆叠芯片

近年来生成式人工智能爆发使得半导体存储器特别是 DRAM 战略价值凸显。鉴于传统二维平面缩小逼近物理极限,依靠垂直堆叠结构提升容量成为了必然趋势。随着半导体制造工艺向纵深延伸,全球企业对垂直维度技术的投入力度显著加大,中国在相关研究领域已获得海外权威机构积极评价。 这种演变源于 AI 模型对数据处理速度提出的新挑战。GPU 及其他处理器虽提升了算力,但若 DRAM 带宽跟不上会导致性能受掣肘,进而形成制约系统效能的壁垒。

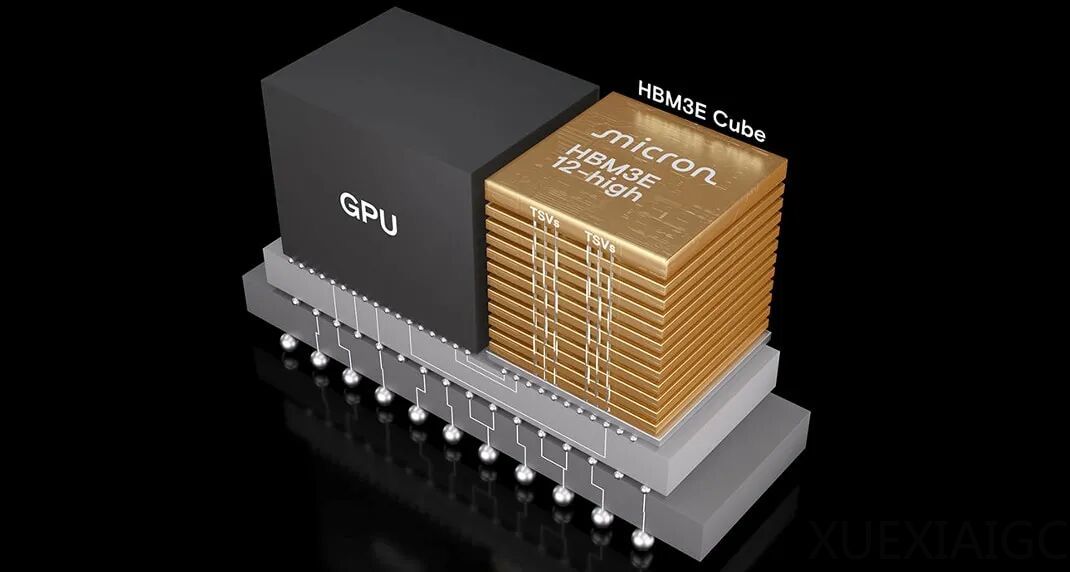

制造商试图通过多层堆叠方案打破此僵局,既追求单位面积容量的倍增,亦关注数据传输延迟的降低。行业内对三维 DRAM 存在不同界定,一种是在单晶硅片上通过前端工艺实现的真正三维结构,旨在极大降低成本。另一种则是利用后段封装堆叠多个独立芯片构成高带宽模块。尽管基于堆叠的高性能版本已在数据中心普及,但全集成方案的商用仍依赖多项尖端材料的成功应用与良率的爬坡。 二者在未来将根据边缘 AI 与超算需求的差异而分化应用,并未发生全面替代效应。

相比于非易失性存储芯片,动态存储器因对瞬时响应速度的敏感性,在进行三维化改造时面临严峻考验。垂直架构的每一层级都必须具备极佳的电气特性以维持高频下的信号完整性,加之热量散逸空间的受限引发了更迫切的热管理系统需求。此外多层堆叠使得修复中间层瑕疵极为困难,这对已知良品率筛选与标准化建设提出了更高指标要求。产业正致力制定统一规范,以期在激烈的市场竞争中确立各自的技术路线并最终稳固其在智能时代基础设施中的地位。随着各厂商研发投入深化,预计在下一轮主流迭代周期内将会显现出明确的市场主导格局与技术标准定型。

原文和模型

【原文链接】 阅读原文 [ 6056字 | 25分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3.5-flash

【摘要评分】 ★★★☆☆