文章摘要

在芯片设计步入“后摩尔时代”的当下,算力需求的爆炸式增长正迫使半导体行业从平面物理极限向多维空间架构寻求突破。在芯片设计步入“后摩尔时代”的当下,算力需求的爆炸式增长正迫使半导体行业从平面物理极限向多维空间架构寻求突破。长期以来芯片性能提升依赖制程突破,摩尔定律失速后,以2.5D/3D封装、Chiplet为代表的先进封装重要性被提升到前所未有的高度,据预测,到2028年2.5D及3D封装将成为第二大先进封装形式。其中2.5D封装通过硅中介层实现水平方向高密度互连,3D封装通过垂直堆叠实现互连密度指数级提升与功耗降低,封装技术早已不再是芯片的“外壳”,而是决定大模型计算效率的核心战场。

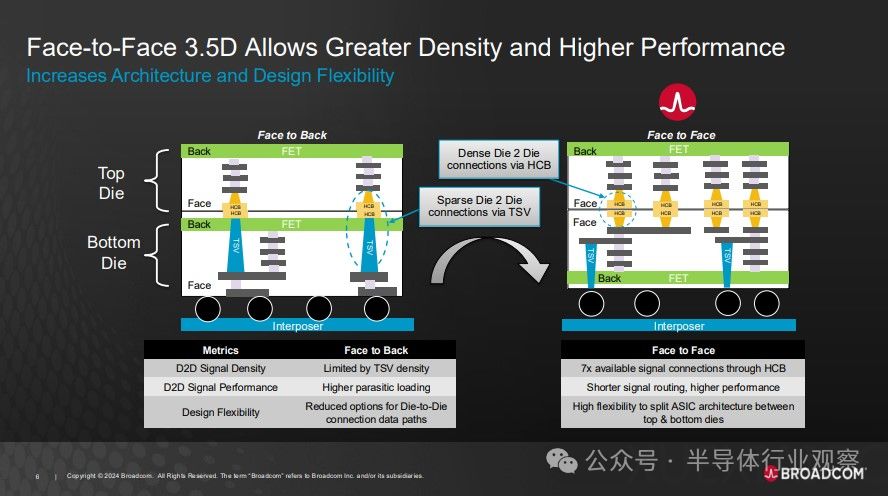

博通已正式交付业界首款基于3.5D XDSiP(超大尺寸系统级封装)平台打造的2nm定制计算SoC给首位客户富士通。这一突破性成果不仅标志着2nm工艺与先进封装的首次合体,更凭借创新的面对面(Face-to-Face, F2F)堆叠技术,将互连信号密度提升了7倍,同时将接口功耗降低了整整10倍。3.5D XDSiP融合了2.5D技术与带F2F堆叠的3D集成,本质是模块化多维堆叠平台,省去传统面背堆叠所需的硅通孔,搭配混合铜键合技术实现无凸块直接互连,互连密度远高于传统方案,还支持将芯片功能拆解为多个Chiplet,为不同功能组件选择最适配的制程,可缩小封装尺寸、降低翘曲风险,支持计算、内存与网络I/O在紧凑形态下独立扩展,适配大规模高效能计算需求。

当前全球半导体巨头均在布局3.5D封装领域,AMD率先实现3.5D封装量产应用于MI300系列AI加速器,实现了性能突破;三星、英特尔也推出了各自的3.5D技术路线;台积电依托CoWoS与SoIC技术为行业提供底层支撑,正加速扩充先进封装产能,推动3.5D封装技术的标准化。博通预计到2027年,基于其3.5D堆叠技术售出的芯片将至少达到100万颗,目前多数客户已在设计中采用该技术。

3.5D封装融合2.5D硅中介层的平面互连优势与3D堆叠的垂直集成能力,是连接当前技术与未来完全3D-IC的桥梁,已经从技术概念走向产业主流,成为全球半导体竞争的新核心。但3.5D封装大规模商用仍面临多重挑战,包括热管理、良率与成本控制、混合铜键合可靠性、时序收敛、EDA工具适配、工艺标准化等,需要全半导体生态的协同创新才能突破。随着技术持续迭代与生态不断完善,3.5D封装将释放异构集成潜力,推动算力硬件向更高密度、更高能效、更灵活定制的方向发展,成为支撑AI、高性能计算等前沿领域突破的核心基石。(全文约760字)

原文和模型

【原文链接】 阅读原文 [ 6287字 | 26分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 doubao-seed-2-0-lite-260215

【摘要评分】 ★★★★☆