文章摘要

【关 键 词】 闪存技术、3D NAND、存储密度、电荷陷阱、气隙集成

NAND闪存技术自20世纪80年代末引入市场以来,已成为数据存储领域的核心支柱。作为非易失性存储器,其高密度特性使其广泛应用于智能手机、数据中心及便携式存储设备。近年来,3D NAND技术通过垂直堆叠存储单元显著提升了存储密度,同时支持人工智能训练所需的大规模数据存储需求。行业通过增加存储层数(目前已超300层)和每个单元的比特数(最高达四比特)持续优化性能,而从浮栅晶体管向电荷陷阱单元的转变进一步降低了单元间干扰,为更高密度铺平道路。

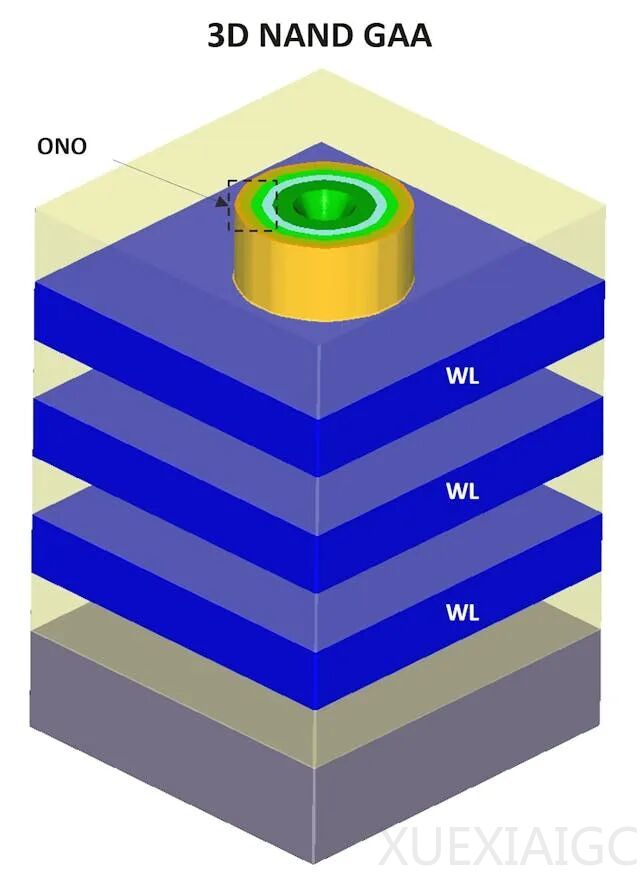

在3D NAND架构中,全环栅(GAA)结构通过垂直堆叠的电荷陷阱单元实现数据存储。电荷陷阱单元采用氧化物-氮化物-氧化物(ONO)堆叠设计,氮化硅层捕获电子以区分“0”和“1”状态。制造过程中,通过交替沉积导体与绝缘层并钻孔形成“通心粉沟道”,实现了垂直沟道包围栅极的结构。随着层数向1000层迈进,工艺挑战集中在深孔蚀刻和材料均匀性控制,而层叠技术(如多次堆叠250层单元)和CMOS键合阵列(CbA)等创新方案正逐步解决这些难题。

Z间距缩放技术成为降低成本的关键路径,通过压缩字线层与氧化层厚度以增加单位高度的存储层数。然而,这一技术可能引发阈值电压波动、电荷横向迁移及功耗上升等问题。研究表明,气隙集成能有效降低单元间静电耦合,imec提出的自对准气隙方案在不影响耐久性的前提下,将干扰敏感度降低30%。此外,电荷陷阱层切割技术通过阻断垂直电荷迁移路径,有望扩大存储窗口,支持更多比特存储,但需突破深孔定向蚀刻的技术瓶颈。

未来,3D NAND的发展将依赖多种技术协同。水平沟道布局和沟槽式架构等新型设计可能突破现有密度极限,而混合键合与多阵列集成方案将进一步优化成本。行业预计到2030年实现100 Gb/mm²的存储目标,但传统架构的收益递减将推动更激进的技术革新。云计算与人工智能的持续需求,正驱动整个存储生态向更高性能、更低成本的维度演进。

原文和模型

【原文链接】 阅读原文 [ 4339字 | 18分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★☆