文章摘要

【关 键 词】 半导体、Chiplet、EDA、系统优化、先进封装

全球半导体产业正在经历从单纯性能竞速向创新驱动范式的深刻转变,Chiplet技术成为这一转型的核心驱动力。通过将复杂系统分解为模块化小芯片并利用先进封装实现异构集成,该技术开辟了提升性能密度的全新路径。然而,这种技术突破需要跨越传统设计方法的边界,要求EDA软件、IP供应商和制造环节形成前所未有的深度协同。

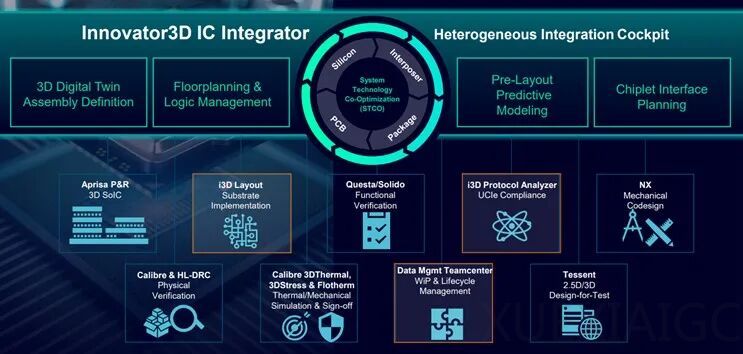

系统级协同成为释放Chiplet潜力的关键突破口。传统线性设计流程难以应对芯片、封装与系统层面的交互影响,西门子EDA提出的系统技术协同优化(STCO)理念贯穿3D IC全流程,构建了从架构规划到签核验证的完整解决方案。其工具链覆盖架构设计阶段的3D数字孪生构建、逻辑验证的硬件仿真加速、物理设计的2.5D/3D结构处理,以及延伸至多芯片系统的物理验证标准。特别值得注意的是其电-热-力多物理场耦合分析方案,通过统一环境模拟功耗、热变形与机械应力的复杂相互作用,实现了晶体管级的精确优化。

在制造端协同方面,西门子EDA与台积电、日月光等领先厂商建立了深度合作伙伴关系。作为台积电3D Fabric联盟创始成员,其工具链不仅适配最先进封装工艺,更参与了3Dblox开放标准的制定。与日月光共同开发的封装设计套件可将开发周期缩短30%-50%,显著提升了设计效率。这种与制造工艺同步就绪的合作模式,确保了技术从实验室到量产的无缝衔接。

生态化建设构成了技术落地的第三大支柱。西门子EDA通过开放计算项目(OCP)参与行业标准制定,建立与IC设计公司的定期技术交流机制,同时与学术界开展工具协作研究,形成了覆盖产业链的技术预见能力。这种多维并举的策略不仅解决了当前的设计挑战,更着眼于未来技术演进的长期需求。

在半导体产业向异质集成转型的关键节点,西门子EDA通过系统级优化、制造协同和生态共建的三维战略,为Chiplet技术商业化提供了从工具链到产业环境的全方位支撑。这种综合解决方案既应对了当下设计复杂度指数增长的现实压力,也为下一代芯片架构的创新奠定了坚实基础,推动整个行业向更高性能密度和更低成本的方向持续演进。

原文和模型

【原文链接】 阅读原文 [ 2125字 | 9分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★★