文章摘要

【关 键 词】 3D集成、无电容架构、高带宽内存、垂直晶体管、氧化物半导体

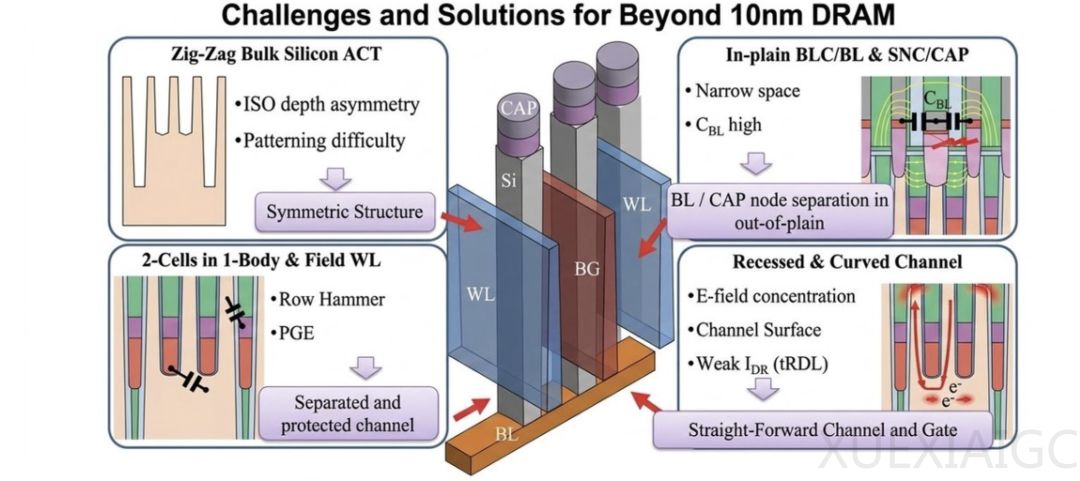

全球半导体行业正因AI与大语言模型的迅猛发展而经历结构性变革,存储芯片从周期性商品转变为AI算力的关键瓶颈,高带宽内存(HBM)需求激增催生“内存超级周期”。传统二维DRAM在10纳米以下节点面临物理极限:电容器纵横比超40:1引发结构缺陷,晶体管尺寸缩小导致栅极漏电、带间隧穿加剧,数据保持时间缩短,刷新功耗上升,构成“内存墙”核心成因。为突破限制,业界分阶段推进技术演进:短期采用4F2垂直沟道晶体管(VCT)作为过渡方案,通过环栅结构提升静电控制能力,面积缩减30%以上;但VCT仍受浮体效应(FBE)、纵向带间隧穿及字线干扰等挑战制约,仅是通向3D集成的“垫脚石”。

中长期方向聚焦单片3D DRAM架构,其中两类路径并行发展:一是基于1T1C单元的垂直堆叠式DRAM(VS-DRAM),延续现有原理但垂直重复阵列,需50层以上堆叠方能超越2D密度,受限于电容占位与多层应力累积;二是彻底取消电容器的无电容架构,如2T0C与3T0C结构,利用晶体管寄生电容或浮体存储电荷,使单片堆叠数百层成为可能。无电容方案结合氧化物半导体沟道材料(如IGZO)展现出显著优势:IGZO具备约3.0 eV宽带隙,关断电流低至阿安级,可延长数据保持时间并大幅降低刷新功耗;其无结结构消除浮体效应与可变保持时间退化问题;且支持低温原子层沉积(ALD),兼容后端工艺,避免热损伤底层电路。华为与中国科学院、铠侠、佐治亚理工等机构已在IEDM与VLSI会议上展示垂直全环沟道IGZO FET、八层水平OCTRAM及逻辑-存储垂直集成等原型成果。

实现3D DRAM量产依赖多项关键工艺协同:晶圆对晶圆(W2W)混合键合技术允许存储阵列与外围电路独立制造后键合,显著提升良率并支持超高密度互连;超高纵横比刻蚀(HARC)需应对50:1至100:1深孔中的弯曲、扭曲与倾斜缺陷,依赖低温刻蚀与脉冲电压技术(PVT)保障轮廓精度;原子层沉积(ALD)成为内壁均匀成膜不可或缺手段;间隙填充转向钼(Mo)、钌(Ru)等低阻新材料;超临界CO₂干燥抑制图案坍塌;晶格失配引发的应力则需通过材料工程缓解。四大厂商路线分化明显:三星推行渐进式策略,2025年验证4F2 VCT,目标2030年商用VS-DRAM;SK海力士依托HBM优势,主推垂直栅极与IGZO材料;美光跳过过渡阶段,直接攻关3D单片集成,凭借早期专利布局抢占先机;铠侠聚焦边缘低功耗市场,以水平堆叠OCTRAM开辟利基路径。值得注意的是,无晶圆厂IP公司如Neo Semiconductor在3D DRAM专利领域位居前列,预示未来价值链将向“制造+授权”混合模式演进。3D DRAM本质非单纯结构升级,而是新材料、新封装与新架构深度融合的技术熔炉,其成败最终取决于低温工艺兼容性、HARC结构精度及异质集成能力的系统性协同。

原文和模型

【原文链接】 阅读原文 [ 7667字 | 31分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3-vl-plus-2025-12-19

【摘要评分】 ★★★☆☆