文章摘要

【关 键 词】 AI芯片、3D堆叠、热管理、HBM、散热优化

Imec近期通过热模拟技术研究了将高带宽内存(HBM)3D堆叠在GPU顶部的可行性,并在2025年IEEE国际电子器件会议(IEDM)上公布了研究成果。结果显示,直接堆叠会导致GPU工作温度飙升至140°C,远超安全阈值。研究团队通过一系列工程优化方案,最终将温差降至接近零,为解决AI计算中的内存带宽瓶颈提供了新思路。

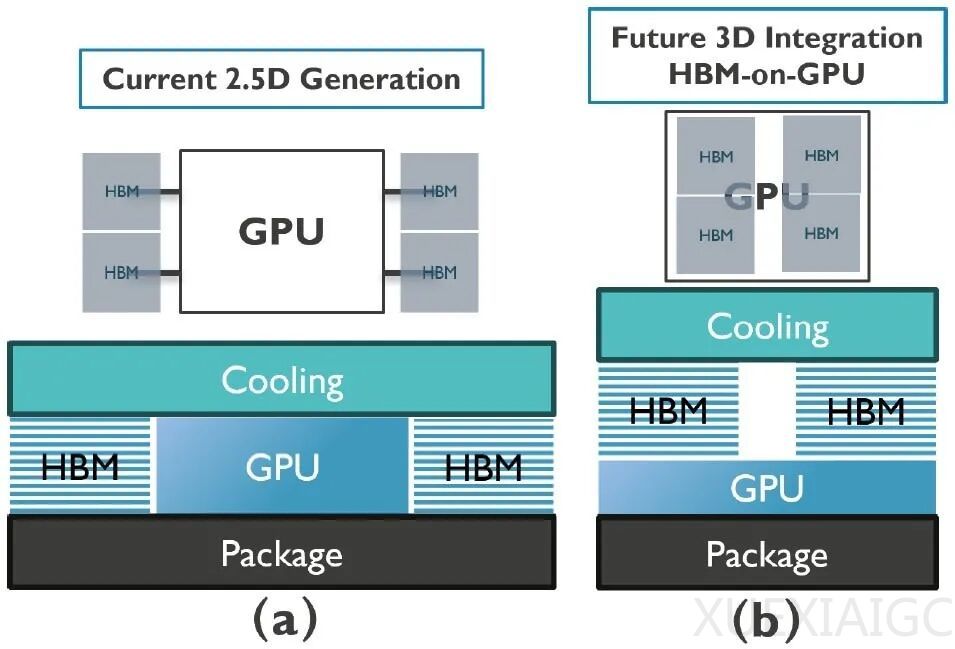

传统2.5D封装中,GPU和HBM通过中介层连接,功耗分别为414瓦和40瓦,峰值温度约70°C。这种设计虽成熟,但限制了多GPU互连和封装尺寸的进一步优化。相比之下,3D堆叠能显著提升带宽并降低延迟,但散热问题成为主要障碍。Imec团队发现,原始3D堆叠方案中,HBM像绝缘体般阻碍热量散发,导致GPU温度翻倍。

研究提出分阶段优化策略:首先移除HBM基片,将内存控制电路集成到GPU中,虽仅降温4°C,但为后续优化奠定基础。其次,合并四个HBM堆叠为两个更宽的结构,减少散热界面,使温度从138°C降至120.4°C。最关键的突破是将GPU频率降低50%,功耗减少114瓦,温度进一步下降至99.2°C。团队指出,尽管计算吞吐量减半,但内存带宽提升4倍可弥补性能损失,在特定AI负载中仍能实现22%-46%的效能提升。

散热材料的创新是另一大亮点。通过减薄HBM顶层芯片、用高导热硅块填充空隙,并采用双面液冷技术,最终使堆叠芯片温度回落至70°C以下。其中,底部散热方案贡献了17°C的降温效果,凸显三维散热设计的重要性。

研究也揭示了产业化挑战:HBM需彻底重构为无基片设计,双宽堆叠将大幅增加制造复杂度;频率折衷方案可能限制芯片通用性。Imec承认,这些变革需全行业协作,尤其对依赖通用DRAM工艺的内存厂商构成挑战。尽管存在争议,该研究为突破”内存墙”提供了技术路径,预示未来AI芯片可能转向以内存带宽为核心的设计范式。

原文和模型

【原文链接】 阅读原文 [ 6115字 | 25分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3-0324

【摘要评分】 ★★★★★