文章摘要

【关 键 词】 硬件评测、内存架构、能效分析、带宽优化、数据中心

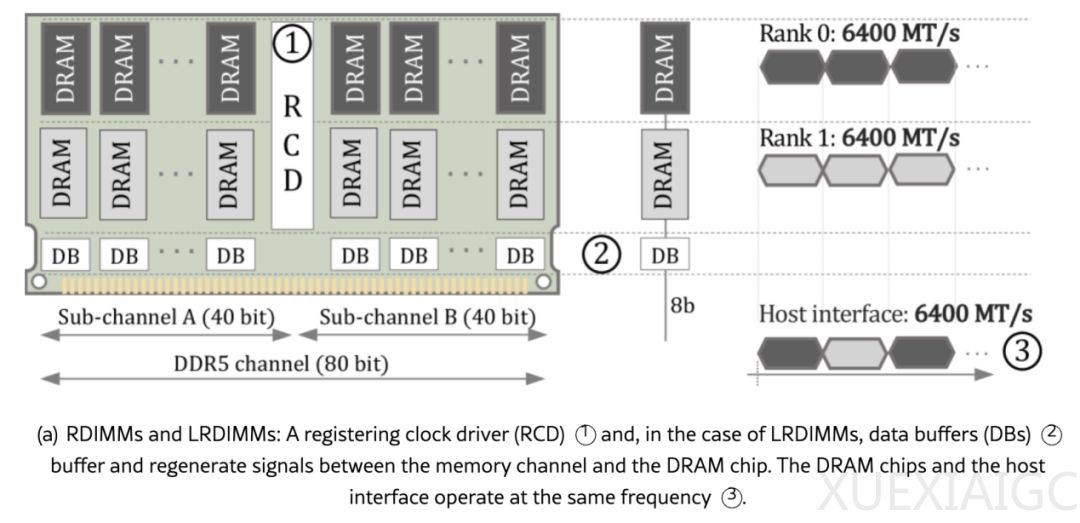

JEDEC近期公布了DDR5 MRDIMM技术的新里程碑,明确了后续模块12800 MT/s及17600 MT/s的研发目标。该规格专为服务器、人工智能系统与高性能计算负载设计,通过引入多路复用数据缓冲区与增强型时钟驱动器架构,在不改变DRAM芯片原生运行频率的前提下,将内存主机通道频率提升一倍,从而突破信号完整性限制并支持更大容量。这种架构创新使数据中心能够在无需立即过渡至最新内存代际标准的情况下,持续挖掘现有平台的性能潜力。

针对配备高端内存模组的生产服务器开展的实测表明,将传统模组替换为新规范设备后,持续内存带宽提升幅度达到41.3%,直接带动带宽密集型应用的性能增长27%至41%。同时,内存访问延迟在全负载区间均有显著下降,优化后的请求调度机制与更高的通道并行性有效缓解了队列冲突,使对延迟敏感的混合工作负载获得稳健改善。这些优势证实了该技术方案作为现有服务器直接替换硬件的可行性。

功耗与能耗评估数据推翻了高带宽升级必然带来显著功耗代价的认知。在双方系统共同覆盖的运行区间内,新方案整机功耗与传统方案基本持平甚至更低,而在其专属的高带宽扩展区域内,性能增益显著超越能耗增量。系统级测试反映,充分利用高带宽特性的负载可使服务器整体能耗降低最高达30%,高效率表现源于存储颗粒以更低原频工作抵消了额外缓冲组件开销,配合处理器底层的写入分配优化策略,实现了能效曲线的大幅上移。

从商业部署视角分析,当前代际设备的市场定价已与同容量传统组件趋同。即便后续迭代产品定价上浮,其带来的单节点吞吐量跃升仍可有效推动算力资源物理整合。通过大幅缩减实际部署的服务器数量,企业能够系统性压减网络互联、软件授权许可与机房占用等综合支出,实现总体拥有成本的深度优化。该技术的规模化落地与架构演进,将为未来十年高算力基础设施的内存升级路径提供明确的工程学依据与经济可行性支撑。

原文和模型

【原文链接】 阅读原文 [ 5003字 | 21分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3.6-plus-2026-04-02

【摘要评分】 ★★★★★