文章摘要

【关 键 词】 CPO、光子集成、系统架构、封装挑战、热管理

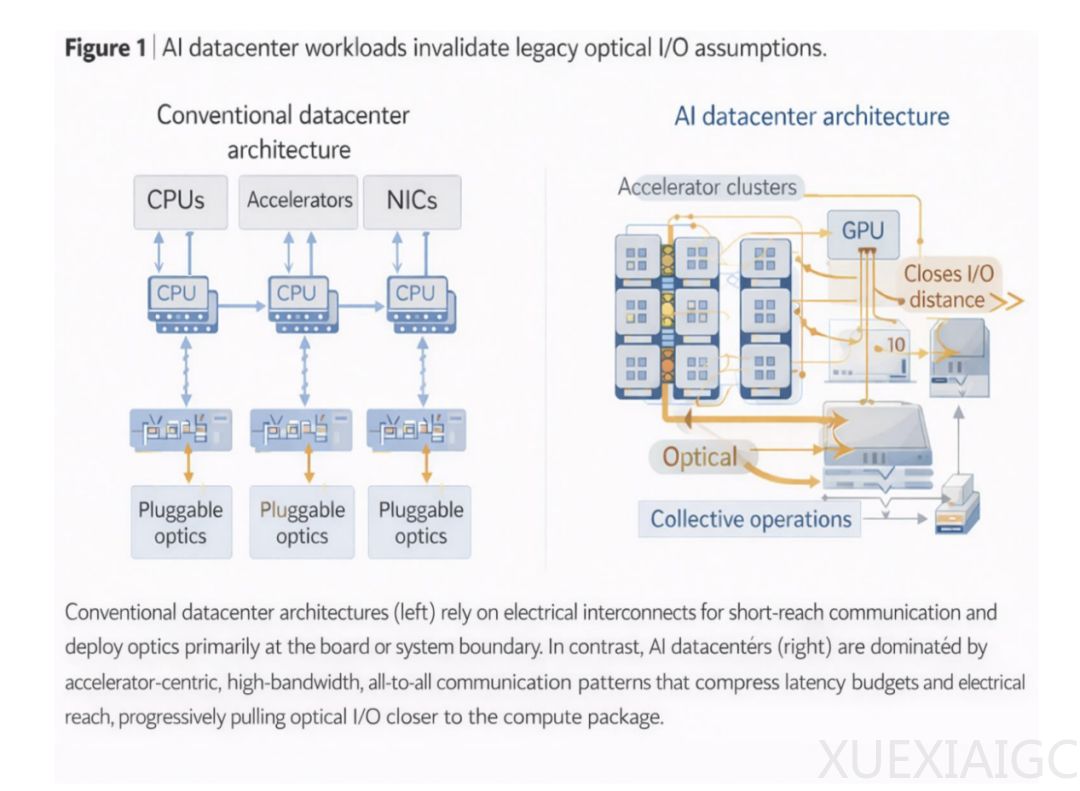

AI工作负载的高密度、低延迟、零容忍特性彻底瓦解了过去“光互连是独立可插拔模块”的假设,使其成为影响架构、封装与可靠性的结构性要素。 传统的光纤I/O依赖通道扩展与数据速率提升来实现带宽增长,但现代AI训练推理中数千加速器间高频全连接流量迫使电气I/O率先成为瓶颈;CPO与3D集成通过缩短走线大幅降低每比特能耗,却同时引入新的系统性挑战:热梯度加剧导致波长漂移,机械应力影响光对准精度,封装内温差波动直接影响谐振器稳定性和链路裕量。此时,单一指标如“每比特能效”被更关键的系统级因素所超越——封装热不稳定性、良率累积与运行脆弱性可能抵消微小的能效增益。

共封装光学器件的本质变化在于:它不再是一种组件优化策略,而是一项系统级架构承诺,重新定义了光子学、电子学与系统设计的边界。 异构集成使得单个光接口故障或性能退化可能引发整套封装失效,维护模型亦需从模块替换转向系统级容错。硅光子学与VCSEL平台之争实质是两种架构理念差异:前者具备长距与高集成潜力但热控严苛,后者适合短距高效部署却受限于波长扩展;二者无绝对优劣,唯在具体系统约束下才显适用性。故障语义同样重构——嵌入式光引擎丧失了传统收发器的独立更换能力,导致修复成本升高且定位难度增大。

封装与异构集成已取代器件性能成为新尺度下的核心扩展约束,良率衰减呈非线性放大,热分布重构限制最高可用带宽,而3D堆叠带来的热路径固化则令后期改造变得极为困难。 热力学效应表明,在高功耗场景下,局部几度温变足以显著削弱谐振器功能;同时,异构芯片组装的乘积良率会随集成密度陡升,直接拉高系统级失败概率。这种复杂性要求采用更稳健的2.5D或中介层架构平衡紧凑性与热管理,从而实现带宽增长平缓但良率稳定的“可持续扩展”。异构整合更催生经济层面的全新考量:先进封装流程推高边际成本,而光-电耦合加深又加剧故障运维开销,最终使得“可重复性”与“兼容性”胜过理论峰值性能。

标准化与模块化已成规模化落地的必要前提,而非附加选项;若缺失内部接口标准,即便chiplet设计也可能滑向定制化碎片化陷阱。 关键接口正由系统外沿向芯片间、封装边界内转移,包括电气连接、光IO几何规范及热机械界面等;只有当这些抽象达成共识,才能保障不同供应商光芯片的互操作性并支撑大规模组装验证。基于Chiplet的方案则提供了创新周期解耦路径——光引擎可独立迭代适配快速演进的加速器设计,避免单片集成因某一环节失效而导致整体项目停滞。该模式唯有配合强标准支持方具现实意义;否则,局部灵活性无法转化为全局可拓展性优势。

面向五年后的成熟场景,成功将体现在“动态适应性”而非极端性能指标上:热感知驱动的智能布局确保真实工况吞吐稳定,异构混合架构精准匹配不同链路等级需求,模块化构建件允许独立更新且不伤及整个系统,以及运维流程与架构深度融合以实现故障容忍而非完全杜绝。 光互连终将回归本质角色——作为AI计算平台不可或缺的一部分参与系统权衡,而非常规特殊解决方案;未来讨论焦点也将从“是否可行”转向“何处、如何、在何程度应部署”。该领域的真正竞争已从光子工艺比拼转向生态体系协作力较量,最终衡量维度将是“能否让光在真实业务流中低调而可靠地运转”,而非“谁拥有最强的峰值数字”。

本领域需警惕盲目追求极致集成,真正决定长期价值的是能否将光学思维深度嵌入到系统架构的每一处约束节点之中,并在性能、可靠性、可维护性与可扩展性之间寻得最佳平衡点。

原文和模型

【原文链接】 阅读原文 [ 9928字 | 40分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3-vl-flash-2026-01-22

【摘要评分】 ★★★★★