文章摘要

【关 键 词】 半导体、芯片验证、EDA平台、人工智能、硬件仿真

随着半导体工艺制程的微缩与系统复杂度加剧,单芯片规模跃升至数百亿门级,市场窗口收窄使得产品上市周期不增反减。面对消费电子与汽车电子的快速迭代压力,工程师急需高效的验证方案。西门子 EDA 推出一整套智能验证平台与硬件仿真系统,通过深度融合人工智能技术与多场景协同验证,重构芯片设计方案,极大缩短了开发周期并提升了验证覆盖率。

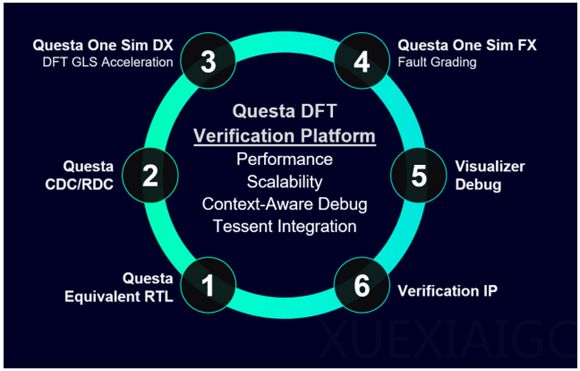

Questa One 智能验证软件以 AI 为驱动,实现了验证流程从被动反应转向主动自优化的智能系统转变。 平台集成了 AI 自动化与分析能力,将仿真时间压缩至以往的六分之一,人工测试工作量大减。针对日益复杂的 DFT 验证挑战,它提供支持静态分析、自动化指令及增强仿真的特性,并与 Tessent 解决方案无缝集成。这种方法有效减少了物理缺陷与老化效应的遗漏,确保芯片满足制造到服役的全周期可靠性,同时降低了因设计反复带来的高昂成本。此外,Calibre Vision AI 等项目进一步巩固了在各个环节的智能化应用。

Veloce CS 硬件仿真系统支持验证工作向全系统与丰富应用场景迈进。 针对 AI 与高性能计算需求,该平台兼容新互联协议,能处理 Arm 及本土处理器等异构系统的核心逻辑。调试工具在统一界面中解决多核匹配难题,无需频繁切换设备。采用 RFRA 技术,用户根据需求选择虚拟模型或硬件加速,有效平衡测试速度与实际性能指标。在某高算力芯片测试案例中,该平台揭示了传统仿真无法捕获的底层硬件缺陷,直接规避了潜在的流片报废风险,切实证明了降低硬件风险的实效价值。

稳固的产业生态网络是进一步提升效益的重要支柱。西门 EDA 联合多家合作伙伴构建“硅 IP 与验证 IP”的完整体系,显著缩短了验证起步时间并规避系统集成风险。在对标主流架构与开放生态的基础上,其平台能适配多种 CPU 设计方案。最终,这一覆盖从内核设计至系统联调的综合能力,使得早期风险识别成为可能,为高端芯片的成功快速量产奠定基础,确保了企业在复杂竞争背景下的商业效率最大化与可持续发展目标。

原文和模型

【原文链接】 阅读原文 [ 2777字 | 12分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 qwen3.5-flash

【摘要评分】 ★★★★☆